NTUST EDA LAB

積體電路的開發與製造產業像盞巨人佇立在人類科技的文明之上;

而我們致力於開發高效、可靠的電子設計自動化演算法,並培育專攻於業的精良人才,

冀使其成為巨人的左膀右臂--將人類舉向更高更遠的世界。

what is EDA?

聽過 EDA(電子設計自動化)嗎?如果你時常關注科技業的新聞,或者你很關心台積電又把摩爾定律的終結推遲了幾年,那你也許常常聽到這個詞。 那什麼是EDA呢?放到 Google Search 上,也許他會問你「你是要查 EDM 嗎?」並且跳出一些 Alan Walker 的歌曲。而在 Wikipedia 中,它對 EDA 的解釋如下:

利用計算機輔助設計(CAD)軟體,來完成超大型積體電路(VLSI)晶片的功能設計、綜合、驗證、物理設計(包括布局、布線、版圖、設計規則檢查等)等流程的設計方式。

這個看似簡單卻涵義廣泛的詞彙並非一夕之間產生的。隨著積體電路製程的發展,從以前一個晶片只包含了屈指可數的電晶體數,到現在動輒上千萬個邏輯閘存在於一個不到指甲大小的晶片當中。 這些晶片製造的複雜程度當然不可同日而語;人類現在若要徒手完成一顆蘋果的處理器而完全不依靠電腦,可能久到連恐龍都可以投胎一次了。於是EDA的產業開始發展了:我們用電腦來輔助積體電路的設計與製造。

簡單來說,我們透過程式語言,開發有效率的演算法,讓人類、甚至電腦都可能要耗時許久才能完成的工作──在可接受的時間內完成。而這些工作,就是積體電路的設計與製造;像是建造一棟摩天大樓,而我們使用 C 語言畫出了設計圖。 所以,若你踏進了EDA領域,也許你可以指著你親朋好友的手機,得意的告訴他:「你的手機的晶片裡,有一段程式碼的變數是我的名字!」並且看看他們欽佩(或是尷尬)的表情。酷吧!

然而 EDA 的範疇何其廣泛,在我們實驗室中,當然也有對 EDA 領域特別擅長的部份!詳情請見 Our interests.

Interests

Research Areas

Physical Design

我們深入探討透過程式語言以及演算法改善積體電路實體設計 ( Physical Design ) 各個階段之效率的可能性,舉凡布圖規劃 ( Floorplanning )、布局 ( Placement )、布線 ( Routing ) 等物理設計階段的加速、品質改善。

Design for Manufacturability

在晶片設計的後端透過演算法提升積體電路在先進製程下的可製造性 ( Design for Manufacturability ),例如微影製程的最佳化 ( 光學鄰近校正 Optical Proximity Correction ) 或虛擬填充 ( Dummy Fill Insertion )。

Machine Learning

隨著人工智慧的風潮蔚起,我們積極研究機器學習 ( Machine Learning )、類神經網路 ( Neural Network ) 等技術應用於解決產業現有問題的可能。

Features

- C / C++

- Algorithm

- Python / Tcl

- Machine Learning / Neural Network

- Data Analysis

- EDA Tools

Advisor

About

- GROUP 積體電路與系統組 Integrated Circuits and Systems

- E-MAIL syfang@mail.ntust.edu.tw

- OFFICE EE-210 校園地圖 campus map

- PHONE +886-2-27376698

EDUCATION

- B.S. Electrical Engineering, National Taiwan University (NTU)

- M.S. Graduate Institute of Electronics Engineering, NTU

- Ph.D. Graduate Institute of Electronics Engineering, NTU

Research Areas

- 電子設計自動化 Electronic Design Automation

- 奈米積體電路實體設計 Physical Design for Nanometer ICs

- 製造可行性/可靠性設計 Design for Manufacturability / Reliability

- 基於機器學習之設計最佳化 Machine Learning-based Optimization

TEACHING

- 超大型積體電路設計導論 Introduction to VLSI Designs

- 數位邏輯設計 Digital Logic Design

- 演算法設計與應用 Algorithm Design and Application

- 奈米積體電路實體設計 Physical Design for Nanometer ICs

Publications

-

Optimal Mixed-Cell-Height Detailed Placement with Discrete Spacing Costs

ACM Transactions on Design Automation of Electronic Systems (TODAES).

-

LithoHoD: A Litho Simulator-Powered Framework for IC Layout Hotspot Detection

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 44, no. 3, pp. 1098–1111, March 2025.

-

Enhanced and Efficient Guiding Template Design for Lamellar DSA with Graph Monomorphism

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 42, no. 11, pp. 4329–4333, November 2023.

-

Keeping Deep Lithography Simulators Updated: Global-Local Shape-Based Novelty Detection and Active Learning

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems (TCAD), vol. 42, no. 3, pp. 1000–1014, March 2023.

-

COALA: Concurrently Assigning Wire Segments to Layers for 2D Global Routing

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems.

-

Demand-Driven Multi-Target Sample Preparation on Microfluidic Biochips With Storage Constraints

ACM Transactions on Design Automation of Electronic Systems (TODAES).

-

Pin Accessibility Prediction and Optimization with Deep Learning-based Pin Pattern Recognition

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems.

-

Placement-Guided Pin Layout Substitution for Routability Optimization

Microelectronics Journal, vol. 114, 2021.

-

From IC Layout to Die Photo: A CNN-Based Data-Driven Approach

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 40, no. 5, pp. 957-970, 2021.

-

Manufacturability Enhancement with Dummy Via Insertion for DSA-MP Lithography Using Multiple BCP Materials

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 40, no. 2, pp. 400-404, 2021.

-

Obstacle-Avoiding Length-Matching Bus Routing Considering Non-Uniform Track Resources

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 28, no. 8, pp. 1881-1892, 2020.

-

Obstacle-Avoiding Open-Net Connector with Precise Shortest Distance Estimation

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 39, no. 5, pp. 1096-1108, 2020.

-

Flip-Chip Routing With I/O Planning Considering Practical Pad Assignment Constraints

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 27, no. 8, pp. 1921-1932, 2019.

-

Printability Enhancement with Color Balancing for Multiple Patterning Lithography

IEEE Transactions on Emerging Topics in Computing, vol. 7, no. 2, pp. 244-252, 2019.

-

Device Array Layout Synthesis With Nonlinear Gradient Compensation for a High-Accuracy Current-Steering DAC

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 37, no. 4, pp. 717-728, 2018.

-

Provably Good Max-Min-m-neighbor-TSP-Based Subfield Scheduling for Electron-Beam Photomask Fabrication

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 26, no. 2, pp. 378-391, 2018.

-

Design Optimization Considering Guiding Template Feasibility and Redundant Via Insertion for Directed Self-Assembly

IEEE Transactions on Circuits and Systems I: Regular Papers, vol. 64, no. 12, pp. 3172-3182, 2017.

-

Cut Mask Optimization With Wire Planning in Self-Aligned Multiple Patterning Full-Chip Routing

IEEE Transactions on Very Large Scale Integration (VLSI) Systems, vol. 25, no. 2, pp. 581-593, 2017.

-

Simultaneous Guiding Template Optimization and Redundant Via Insertion for Directed Self-Assembly

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 36, no. 1, pp. 156-169, 2017.

-

Overlay-aware Detailed Routing for Self-Aligned Double Patterning Lithography Using the Cut Process

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 35, no. 9, pp. 1519-1531, 2016.

-

Stitch-Aware Routing for Multiple E-Beam Lithography

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 34, no. 3, pp. 471-482, 2015.

-

A Novel Layout Decomposition Algorithm for Triple Patterning Lithography

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 33, no. 3, pp. 397-408, 2014.

-

Graph-Based Subfield Scheduling for Electron-Beam Photomask Fabrication

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 32, no. 2, pp.189-201, 2013.

-

Native-Conflict and Stitch-Aware Wire Perturbation for Double Patterning Technology

IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems, vol. 31, no. 5, pp. 703-716, 2012.

-

MIA-aware FinFlex Cell Legalization with Power-Driven Cell Version Substitution

ACM/IEEE Design Automation Conference (DAC-2025), San Francisco, CA, June 2025.

-

Secondary-Power-Cell-Aware Detailed Placement in Multiple Power Domain Designs

ACM/IEEE Design Automation Conference (DAC-2025), San Francisco, CA, June 2025.

-

Pin Access-aware Multiple Via Pillar Co-Design for Routability Optimization

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-25), Tokyo, January 2025.

-

Paired-Spacing-Constrained Package Routing with Net Ordering Optimization

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-25), Tokyo, January 2025.

-

Via Fabrication with Multi-Row Guiding Templates Using Lamellar DSA

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-25), Tokyo, January 2025.

-

CPONoC: Critical Path-aware Physical Implementation for Optical Networks-on-Chip

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-25), Tokyo, January 2025.

-

SMT-based Layout Synthesis for Silicon-based Quantum Computing with Crossbar Architecture

IEEE/ACM International Conference on Computer-Aided Design (ICCAD-2024), Newark, NJ, October 2024.

-

(Invited Paper) Overview of 2024 CAD Contest at ICCAD

IEEE/ACM International Conference on Computer-Aided Design (ICCAD-2024), Newark, NJ, October 2024.

-

Concurrent Detailed Routing with Pin Pattern Re-generation for Ultimate Pin Access Optimization

ACM/IEEE Design Automation Conference (DAC-2024), San Francisco, CA, June 2024.

-

Practical Mixed-Cell-Height Legalization Considering Vertical Cell Abutment Constraint

ACM International Symposium on Physical Design (ISPD-2024), Taipei, Taiwan, March 2024.

-

Active Learning-based Practical Power Estimation Considering Multi-Cycle Paths

Workshop on Synthesis and System Integration of Mixed Information Technologies (SASIMI-2024), Taipei, Taiwan, March 2024.

-

Spacing Cost-aware Optimal and Efficient Mixed-Cell-Height Detailed Placement for DFM Considerations

IEEE/ACM International Conference on Computer-Aided Design (ICCAD-2023), San Francisco, CA, October 2023.

-

Lamellar DSA-aware Detailed Routing Considering Double Patterning and Short Template Minimization

ACM/IEEE Design Automation Conference (DAC-2023), San Francisco, CA, July 2023.

-

Pin Access-Oriented Concurrent Detailed Routing

ACM International Symposium on Physical Design (ISPD-2023), virtual conference, March 2023.

-

Advanced Design Methodologies for Directed Self-Assembly (Invited)

ACM International Symposium on Physical Design (ISPD-2023), virtual conference, March 2023.

-

Mitigating Layout Dependent Effect-induced Timing Risk in Multi-Row-Height Detailed Placement

IEEE/ACM Design Automation and Test in Europe (DATE-2023), Antwerp, Belgium, April 2023.

-

Data-Driven Approaches for Process Simulation and Optical Proximity Correction (Invited)

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-23), Tokyo, January 2023.

-

MIA-aware Detailed Placement and VT Reassignment for Leakage Power Optimization

ACM/IEEE Asia South Pacific Design Automation Conference (ASP-DAC-23), Tokyo, January 2023.

-

A Robust Quantum Layout Synthesis Algorithm with a Qubit Mapping Checker

IEEE/ACM International Conference on Computer-Aided Design (ICCAD-2022), San Diego, CA, October 2022.

-

SpeedER: A Supervised Encoder-Decoder Driven Engine for Effective Resistance Estimation of Power Delivery Networks (Best Paper Award)

ACM/IEEE Workshop on Machine Learning for CAD (MLCAD-2022), Snowbird, UT, September 2022.

-

RobustONoC: Fault-Tolerant Optical Networks-on-Chip with Path Backup and Signal Reflection

IEEE International Symposium on Quality Electronic Design (ISQED), 2021.

-

Machine Learning-based Structural Pre-route Insertability Prediction and Improvement with Guided Backpropagation

26th Asia and South Pacific Design Automation Conference (ASP-DAC), 2021.

-

COALA: Concurrently Assigning Wire Segments to Layers for 2D Global Routing

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020.

-

Meshed Stack Via Design Considering Complicated Design Rules with Automatic Constraint Generation

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020.

-

Guiding Template Design for Lamellar DSA with Multiple Patterning and Self-Aligned Via Process

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2020.

-

Stitch-Aware Routing Considering Smart Boundary for Multiple E-Beam Lithography

International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2020.

-

Lookahead Placement Optimization with Cell Library-based Pin Accessibility Prediction via Active Learning

ACM International Symposium on Physical Design (ISPD), 2020.

-

Via Pillar-aware Detailed Placement

ACM International Symposium on Physical Design (ISPD), 2020.

-

FIST: A Feature-Importance Sampling and Tree-Based Method for Automatic Design

25th Asia and South Pacific Design Automation Conference (ASP-DAC), 2020.

-

Capacitance Minimization Clock Synthesis with Blockage-Avoiding Hybrid-Structure Network

International Symposium on Intelligent Signal Processing and Communication Systems (ISPACS), 2019.

-

Color Balancing-aware Non-Stitch Routing for Multiple Patterning Lithography

Workshop on Synthesis And System Integration of Mixed Information technologies (SASIMI), 2019.

-

Pin Accessibility Prediction and Optimization with Deep Learning-based Pin Pattern Recognition

56th ACM/IEEE Design Automation Conference (DAC), 2019.

-

Routability-Driven Macro Placement with Embedded CNN-Based Prediction Model

Design, Automation & Test in Europe Conference & Exhibition (DATE), 2019.

-

Deep Learning-Based Framework for Comprehensive Mask Optimization

24th Asia and South Pacific Design Automation Conference, 2019.

-

RouteNet: Routability Prediction for Mixed-Size Designs Using Convolutional Neural Network

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2018.

-

Obstacle-Avoiding Open-Net Connector with Precise Shortest Distance Estimation

55th ACM/ESDA/IEEE Design Automation Conference (DAC), 2018.

-

PlanarONoC: Concurrent Placement and Routing Considering Crossing Minimization for Optical Networks-on-Chip

55th ACM/ESDA/IEEE Design Automation Conference (DAC), 2018.

-

Guiding Template-Induced Design Challenges in DSA-MP Lithography

IEEE Computer Society Annual Symposium on VLSI (ISVLSI), 2018.

-

Triple Patterning Lithography-aware Detailed Routing Ensuring Via Layer Decomposability

International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2018.

-

Flip-chip Routing with IO Planning Considering Practical Pad Assignment Constraints

23rd Asia and South Pacific Design Automation Conference (ASP-DAC), 2018.

-

Simultaneous Template Assignment and Layout Decomposition Using Multiple BCP Materials in DSA-MP Lithography

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2017.

-

Design Optimization for Directed Self-Assembly

IFIP/IEEE International Conference on Very Large Scale Integration (VLSI-SoC), 2017.

-

Minimizing Cluster Number with Clip Shifting in Hotspot Pattern Classification

54th ACM/EDAC/IEEE Design Automation Conference (DAC), 2017.

-

Guiding Template-aware Routing Considering Redundant Via Insertion for Directed Self-Assembly

22nd Asia and South Pacific Design Automation Conference (ASP-DAC), 2017.

-

Printability Enhancement with Color Balancing for Multiple Patterning Lithography

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2016.

-

Design Optimization Considering Guiding Template Feasibility and Redundant via Insertion for Directed Self-Assembly

IEEE Asia Pacific Conference on Circuits and Systems (APCCAS), 2016.

-

Trim Mask Optimization for Hybrid Multiple Pattering Lithography

International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2016.

-

Overlay-aware Layout Legalization for Self-Aligned Double Patterning Lithography

International Symposium on VLSI Design, Automation and Test (VLSI-DAT), 2016.

-

Lossless Compression Algorithm Based on Dictionary Coding for Multiple E-Beam Direct Write System

Design, Automation & Test in Europe Conference & Exhibition (DATE), 2016.

-

Simultaneous Guiding Template Optimization and Redundant Via Insertion for Directed Self-Assembly

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2015.

-

Provably Good Max-Min-m-neighbor-TSP-Based Subfield Scheduling for Electron-Beam Photomask Fabrication

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2015.

-

EUV and E-Beam Manufacturability: Challenges and Solutions

52nd ACM/ESDA/IEEE Design Automation Conference (DAC), 2015.

-

Cut Mask Optimization with Wire Planning in Self-Aligned Multiple Patterning Full-Chip Routing

20th Asia and South Pacific Design Automation Conference (ASP-DAC), 2015.

-

Layout Decomposition for Spacer-is-Metal (SIM) Self-Aligned Double Patterning

20th Asia and South Pacific Design Automation Conference (ASP-DAC), 2015.

-

Overlay-aware Detailed Routing for Self-Aligned Double Patterning Lithography Using the Cut Process

51st ACM/IEEE Design Automation Conference (DAC), 2014.

-

Stitch-Aware Routing for Multiple E-Beam Lithography

50th ACM/IEEE Design Automation Conference (DAC), 2013.

-

Simultaneous OPC- and CMP-aware Routing Based on Accurate Closed-Form Modeling

ACM International Symposium on Physical Design (ISPD), pp. 77-84, 2013.

-

Simultaneous Flare Level and Flare Variation Minimization with Dummification in EUVL

49th ACM/ESDA/IEEE Design Automation Conference (DAC), pp. 1175-1180,2012.

-

A Novel Layout Decomposition Algorithm for Triple Patterning Lithography

49th ACM/ESDA/IEEE Design Automation Conference (DAC), pp. 1181-1186,2012.

-

Graph-Based Subfield Scheduling for Electron-Beam Photomask Fabrication

ACM International Symposium on Physical Design (ISPD), pp. 9-16, 2012.

-

Redundant-Wires-Aware ECO Timing and Mask Cost Optimization

IEEE/ACM International Conference on Computer-Aided Design (ICCAD), pp. 381-386, 2010.

Awards

"Awesome !!!!"

面對來自世界各地同一領域的菁英,碩士生楊凱筌、江昀哲與張家泓脫穎而出,在著名的 EDA 程式競賽 ICCAD CAD Contest 的 Problem C (Timing-Aware Fill Insertion) 上奪得了世界第三,前往美國聖地牙哥領獎。

Kai-Chuan Yang, Yun-Jhe Jiang and Leo Chang finally got the better of many opponents from global and won the Third Place of Problem C (Timing-Aware Fill Insertion) in the contest. The ceremony is held at San Diego, US.

"Thanks for the affirmation from the contest's evaluator."

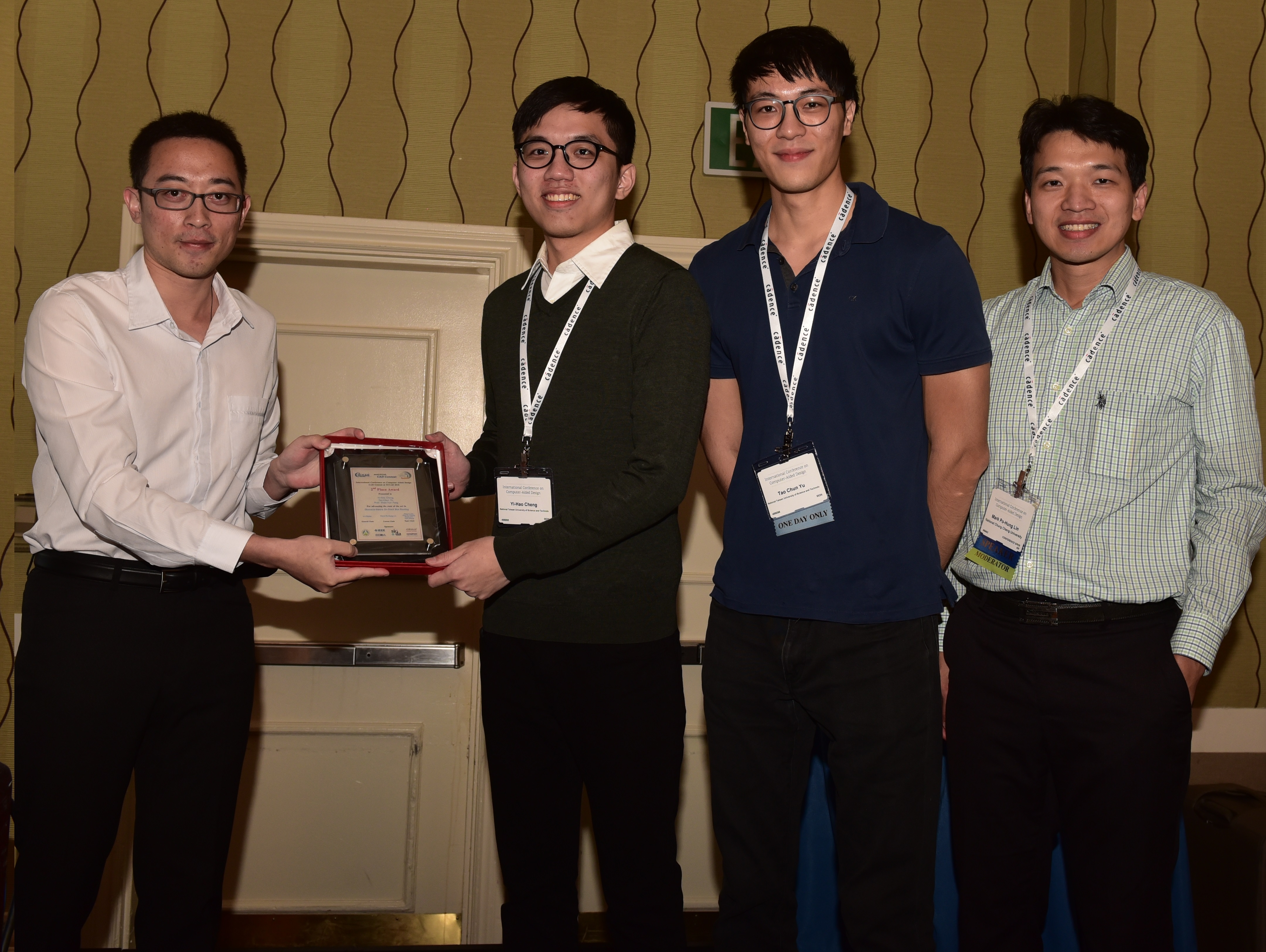

碩士生鄭依豪與博士生禹道軍也不惶多讓,在 2018 年的 ICCAD CAD Contest 的 Problem B (Obstacle-Aware On-Track Bus Routing) 中,運用精巧的演算法技巧,技壓群雄,奪得世界第二的殊榮。

Yi-Hao Cheng and Tao-Chun Yu also won the Second Place of Problem B (Obstacle-Aware On-Track Bus Routing) in 2019 ICCAD CAD Contest.

"It's a piece of cake since we have a genius advisor."

碩士生張家泓、楊凱筌與江昀哲在 2018 年 ICCAD CAD Contest 程式競賽的推廣題 Problem E (Color-aware Routing for Double Patterning) 中的表現獨占鰲頭,榮獲第一名。

Leo Chang, Kai-Chuan Yang and Yun-Jhe Jiang is the champion of Problem E (Color-aware Routing for Double Patterning) in the 2018 ICCAD CAD contest. The ceremony is held at Tainan, Taiwan.

"We made it!"

專題生梁家睿、陳鋐霖、石文緯、洪裕堃、鍾瑋紘、金真湖在 2018 年 ICCAD CAD Contest 程式競賽的推廣題 Problem E (Color-aware Routing for Double Patterning) 中表現優異,榮獲佳作。

Contact

- 10607 臺北市大安區基隆路 4 段 43 號 第二教學大樓(T2) - 403 室 校園地圖

- Room 403, T2 Building, No.43, Keelung Rd., Sec.4, Da'an Dist., Taipei City 10607, Taiwan (R.O.C.) Campus map

- +886-2-27333141 EXT. 7939